はじめに

FPGAやデジタル回路設計を進めると必ず出てくるのが「クロックドメイン」という言葉です。

「クロックドメインとは何か?」、「なぜ大事なのか?」、「どう対応すればいいのか?」を一つ一つ解説し、設計で迷わないように実用上のポイントをお伝えします。

1. クロックドメインとは何か?

「クロックドメイン」とは、同じクロック信号で動作する回路のまとまりを意味します。

FPGAでは、異なるクロックを使うことがよくあり、これが設計の複雑さの原因にもなります。

例:

- FCLK_CLK0 → 125MHz(周波数)で動作する回路

- FCLK_CLK1 → 250MHz(周波数)で動作する回路

これらのクロックは別々のクロックドメインになります。

2. クロックドメインが違うと何が問題なのか?

クロックドメインが異なると、次のような問題が発生します:

- タイミングのずれ

異なるクロックでは、データが送られた瞬間と受け取る瞬間のタイミングが合わず、データが破損することがあります。- 例:125MHzのクロックで「1」を送ったが、250MHzのクロックでは読めずに不安定な状態になる。

- メタステーブル

異なるクロックドメイン間でデータをやり取りすると、信号が「0」でも「1」でもない不安定な状態(メタステーブル)になることがあります。

3. クロックドメインの具体例

FPGA設計では、クロックドメインの違いがよく見られます。

ケース1: 単一クロックドメイン

同じクロックで全体を動かす場合は問題なし!

- FCLK_CLK0(125MHz)

- すべてのIPコア、インタフェースがこのクロックで動く

設計ポイント:

- クロックを「1本」に統一することで同期の問題は起きません。

ケース2: 複数のクロックドメイン

例えば、以下のように動く場合:

- FCLK_CLK0 → 125MHz(AXIインタフェース)

- FCLK_CLK1 → 250MHz(高速処理IP)

設計ポイント:

- クロックドメイン間のデータ転送には対策が必要です。

- FIFO(First-In First-Out Buffer)を使う

- 同期レジスタを挟んで信号を安定させる

4. 実際にVivadoでの確認方法

クロックソースの確認

Vivadoでは「PS(Processing System)」から生成されるクロックがよく使われます。

- FCLK_CLK0:125MHz

- FCLK_CLK1:250MHz

これらのクロックを各IPコアやAXIバスに接続することで、クロックドメインを設定します。

どのクロックが供給されているか?

各IPコアやAXIインタフェースには「ACLK」や「CLK」のピンがあり、ここにどのクロックドメインが供給されているか確認できます。

- M_AXI_GP0_ACLK →

FCLK_CLK0 - S_AXI_HP0_ACLK →

FCLK_CLK1

5. クロックドメイン間の設計のコツ

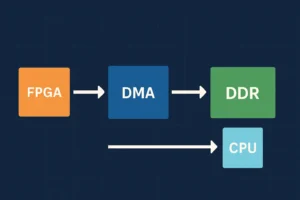

複数のクロックドメインを使う場合、次の対策が必要です:

1. FIFOを使ったデータ転送

FIFO(First-In First-Out)バッファは、データを安全にクロックドメイン間で転送するための回路です。

- 書き込み側 → クロックA

- 読み出し側 → クロックB

FIFOが自動的にデータをバッファし、ドメイン間のタイミング問題を解消します。

2. 同期レジスタ

データや制御信号が単一ビットの場合は、同期レジスタを使って安定化させます。

→ 2段または3段のフリップフロップを使うことで、メタステーブルを回避します。

6. まとめ:設計で困らないためのポイント

- 単一クロックドメイン:シンプルで設計が楽

- 複数クロックドメイン:FIFOや同期レジスタを使って対策する

- クロックソース:Vivadoの

FCLK_CLKや外部クロックを確認 - ACLK や CLK ピンがどのクロックドメインに紐づいているか確認する

次にすべきこと

Vivadoでブロックデザインを開き、クロックの接続やACLKの供給元を確認してみましょう。

複数のクロックドメインが存在する場合は、FIFOを追加する練習もしてみてください!