RTLの基本的な意味と役割

FPGAやASICの設計を始めると、「RTL(Register Transfer Level)」という言葉に出会います。初心者の方にとって、この言葉はとっつきにくく、HDL(Hardware Description Language)とどう違うのか疑問に感じることが多いかもしれません。

RTLとは「レジスタ転送レベル」を意味し、ハードウェア設計における抽象レベルの一つです。

ハードウェア設計では、設計の抽象度によって以下のような段階に分けられます。

| レベル | 説明 |

|---|---|

| ビヘイビアレベル | アルゴリズムや動作を抽象的に記述する段階 |

| RTL(レジスタ転送) | クロックとレジスタを基準に動作を定義する段階 |

| ゲートレベル | 論理ゲート(AND, OR, NOTなど)で表現 |

| トランジスタレベル | MOSFETなど物理素子の接続を記述するレベル |

この中でRTLは「実際の回路として実装可能な現実的な設計レベル」にあたります。

HDL(たとえばVerilogやVHDL)で書かれたコードはこのRTLレベルを表現するために用いられますが、HDLのすべてがRTLというわけではありません。

RTLに該当するのは、クロックの動きに従ってレジスタ間でデータがどのように移動するかを定義した部分です。

RTL記述とはどういうものか

具体的にどのような記述がRTLなのかを理解するためには、「クロックとレジスタ」を中心に考えることが重要です。

RTL記述とは、クロックに同期してレジスタの値がどのように変化するかを定義したものです。

例えば、以下のVerilogコードはRTL記述の代表例です。

always_ff @(posedge clk) begin

if (reset)

count <= 0;

else

count <= count + 1;

end

このように、クロックの立ち上がり(posedge clk)に応じてレジスタcountの値が変化する動作を記述しています。時間軸に従った動作、つまり「いつ・どこに・何を」送るかを明示的に記述していることがRTLの本質です。

一方で、以下のような宣言はRTLとは言いません。

logic [7:0] count;

parameter MAX = 255;

これは信号の定義や定数の宣言であり、回路の動作そのものを表してはいません。

また、assign文やalways_combによる記述も、組み合わせ論理を表しているだけであり、クロックとレジスタに基づいた時間制御が含まれていなければRTLとは見なされません。

RTLという概念が必要な理由

HDLを書く際に、特にRTLと明記する必要があるのかと疑問に思う方も多いと思います。しかし、RTLという概念は、設計の進行段階を明確にし、ツールやチームとの連携を円滑にするために不可欠です。

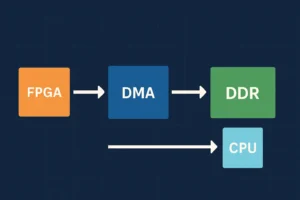

ハードウェア設計のフローには以下のような段階があります。

- アルゴリズム設計(ビヘイビア記述、C言語など)

- RTL記述(HDLでの設計)

- 論理合成(ゲートレベルへの変換)

- 配置配線、実装、ビットストリーム生成

この中で、論理合成や実装に進めるのは、RTLレベルで記述されたコードだけです。

ビヘイビア記述ではシミュレーションは可能でも、合成はできません。

また、開発の進捗管理や品質保証の観点でも、「このコードはRTLレベルで完成しているのか?」という問いが重要になります。

そのため、単にHDLを書いているだけではなく、レジスタ転送やタイミング制御が正しく記述されているかどうかを常に意識する必要があります。

このように、RTLという用語は「物理的な回路として成立する設計段階に達しているかどうか」を判断するラベルとして機能しているのです。

実際に使われる文脈での「RTL」

RTLという言葉は、設計現場やツールの操作、ドキュメントなど様々な場面で登場します。以下は代表的な使用例です。

RTL設計

HDLコードの中でも、レジスタとクロックを用いて回路動作を定義している部分を指します。

「このモジュールはRTLまで設計済みですか?」という確認は、「実装できる形になっていますか?」という意味です。

RTLシミュレーション

クロックやタイミング制御を含んだ動作をシミュレーションで確認するフェーズです。

このシミュレーションが通って初めて、論理合成・実装へと進む準備が整ったと判断されます。

なお、「RTLシミュレーション」という言葉は、「論理シミュレーション(Logic Simulation)」とほぼ同義ですが、少しだけニュアンスが異なります。

論理シミュレーションはHDL記述全般を対象にしたシミュレーションを指す一方で、RTLシミュレーションは“合成可能なRTL記述に対して行うシミュレーション”を特に強調している言い方です。

つまり、#10のような時間遅延や非合成記述を含まない、ハードウェアとして成立する前提のコードに対する動作確認という意味合いを持ちます。

Vivadoなどのツールでは「Simulation」として表記されており、「RTLシミュレーション」という表現は設計の抽象度を意識して使われる用語です。

そのため、日常のツール操作では「論理シミュレーション」と呼び、ドキュメントや技術的な説明では「RTLシミュレーション」と表現されることがあります。

RTLダイアグラム/RTLビュー

Vivadoなどの設計ツールでは、HDLコードから自動で回路図を生成する機能があります。これが「RTLビュー」です。

レジスタ・信号線・論理演算の関係が視覚的に確認できるため、設計ミスの早期発見にも役立ちます。

これらの文脈からも分かる通り、「RTL」という言葉は単なる技術用語ではなく、実務に直結する重要な概念です。

まとめ:RTL理解が設計の地盤になる

FPGAの設計において、RTLの理解は避けて通れません。

HDLコードの中で、レジスタとクロックに支配された部分こそが、実際に動作する「回路の本体」です。

その部分を正しく記述する力こそが、FPGA開発における基礎体力となります。

RTLという言葉を見かけたときは、「設計が回路として成立しているかどうかを確認するための目印」として受け取ってください。

そして、自分が書いたHDLコードが“RTLになっているか”を常に意識することが、開発者としての質を大きく左右します。

最初は難しく感じるかもしれませんが、一度身につけば、RTLの考え方はすべての設計判断の基準になります。

自分の設計がいつ、どこで、どう動くか。それを読み解く力こそが、RTL理解の本質です。