Red Pitayaは、柔軟で高精度な任意波形発生器(ASG: Arbitrary Signal Generator)を備えています。本記事では、Red PitayaのASGを活用するための基礎を解説します。波形生成の仕組みと、各パラメータの考え方を理解することで、より効果的にRed Pitayaを利用できるようになります。

ASGの基本構成

Red PitayaのASGは、次のような構成で動作します:

- 波形データバッファ(

BUF)- 波形データは、このバッファに格納されます。

- サンプリングポイント(データの個数)で構成され、ループ再生やデータの一部のみ再生する設定が可能です。

- 制御パラメータ

- 出力周波数、振幅、オフセット、繰り返し条件などを設定します。

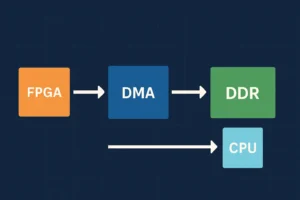

- FPGA内部で直接制御する仕組みのため、高速で柔軟な設定が可能です。

- 出力DAC

- バッファのデータをDACを通して出力します。

- 出力精度や波形の滑らかさは、データバッファや設定パラメータに依存します。

主なパラメータと役割

以下のコードに登場する変数を使って、パラメータの具体例を説明します。

# 波形データのオフセットアドレス

WAVEFORM_BUFFER_OFFSET = 0x10000

# 制御パラメータ

SIZE_REG = 0x08 # 波形データサイズ

STEP_REG = 0x10 # 波形ステップサイズ

AMP_OFFSET_REG = 0x04 # 振幅とオフセット

WRAP_ONCE_REG_OFFSET = 0x00 # 繰り返し設定

1. 波形サイズ(SIZE_REG)

波形データバッファの有効ポイント数を設定します。

- 値の意味: バッファ内の波形データ数(サンプル数)。多ければ多いほど正確な波形を生成できますが、1周期に必要な時間が増えます。

- 例:

波形データがsize = 1024なら、1周期で1024個のサンプルを参照します。

2. ステップサイズ(STEP_REG)

波形データバッファを参照する間隔を設定します。

- 値の意味: ステップが小さいほど細かくデータを読み出します。ステップを大きくすると、データを飛ばして参照します。

- 例:

ステップをstep = 2にすると、バッファ内の2つおきのデータを使用します。

3. 振幅とオフセット(AMP_OFFSET_REG)

波形のスケール(振幅)と直流オフセット(DC)を設定します。

- 振幅: 波形の最大値を調整します(例: 0.5Vから1.0Vなど)。

- オフセット: 波形全体を上下にシフトします。

4. 繰り返し設定(WRAP_ONCE_REG_OFFSET)

波形をループ再生するか、単発出力するかを決定します。

wrapフラグ: 有効にするとバッファのデータを繰り返します。- 例:

wrap = 1(ループ再生)wrap = 0(1周期で停止)

5. 波形データバッファ

波形データそのものを格納します。

- Pythonでの例:

waveform_data = [0x1FFF if i % 2 == 0 else 0x0000 for i in range(1024)]この場合、波形は1周期に1024点で構成される矩形波です。

波形の周波数を決める

波形周波数は、次の式で計算されます

$$f = \frac{\text{クロック周波数}}{\text{size} \times \text{step}}$$

例: 1MHzの正弦波を生成

- クロック周波数: 250MHz(DACのクロック)

- size: 1024(1周期のデータポイント数)

- step: 244(ポイントの間隔)

計算すると:

$$ f=250,000,0001024×244≈1,000,000 Hzf = \frac{250,000,000}{1024 \times 244} \approx 1,000,000 \, \text{Hz}$$

繰り返し回数と遅延

ASGは単発または繰り返し波形の出力が可能です。ここでは、RedPitayaのチュートリアルにある具体的な変数名を使って説明します。

1. ncyc(周期内サイクル数)

1回の波形出力で、何周期分の波形を生成するかを設定します。

2. rnum(繰り返し回数)

波形出力全体の繰り返し回数を設定します。

3. rdly(遅延時間)

波形出力の繰り返し間隔を設定します。

- 単位: DACクロック(1クロック = 4ns)。

応用例: パルス列の生成

- 10回繰り返すパルス波(

rnum = 10) - 各パルス間に1msの遅延(

rdly = 250,000)

波形生成における最適化の考え方

- 周波数を基準に設定:

- 目標周波数に応じて

sizeとstepを計算。 - 必要に応じて

wrapを有効にして波形をループ再生。

- 目標周波数に応じて

- 波形の滑らかさを考慮:

- 三角波や矩形波など単純な波形では、

sizeを小さくしても問題ない。 - 正弦波など複雑な波形では、

sizeを大きくして高精度に。

- 三角波や矩形波など単純な波形では、

- ハードウェアの制約に注意:

- バッファサイズ(

RSZ)やDACクロックに基づき、実現可能な周波数と波形を計算。

- バッファサイズ(

まとめ

Red PitayaのASGは、波形生成の基本を理解し、柔軟に制御できる強力なツールです。本記事で紹介したパラメータの役割と設定方法を活用することで、自分の目的に合った波形を効率的に生成できます。

ASGの操作はDACやデジタル信号処理の基本的な知識を学ぶ良い機会でもあります。まずは単純な波形を試し、次第に複雑な設定に挑戦してみてください!