AXI (Advanced eXtensible Interface) は、FPGA や SoC (システム・オン・チップ) デザインにおける重要なバスインターフェースです。この記事では、AXI の概要、主な特徴、および実際の導入ケースを解説します。Red Pitaya やその他の FPGA プロジェクトにおける AXI の役割も含めています。

AXI の概要

AXI は ARM 社が開発した AMBA (Advanced Microcontroller Bus Architecture) の一部で、高性能なチップ内通信を実現するためのインターフェース規格です。この規格は、特に FPGA や SoC のデザインにおいてよく使われます。

AXI の目的

AXI の主な目的は、プロセッサシステム (PS) とプログラマブルロジック (PL)間の高性能なデータ通信を実現することです。その特徴は以下の通りです。

- 高スループット: 高速なデータ転送が可能です。

- パイプライン化: 複数のトランザクションを平行して処理できます。

- バースト転送: 一度のリクエストで複数のデータを転送でき、バスの効率を高めます。

- フルデュプレックス: 読み取りと書き込みを同時に独立して行うことができます。

AXI の構造

AXI は通常、以下の5つの独立したチャネルから構成されます。

- 読み取りアドレスチャネル (Read Address Channel)

- 読み取りデータチャネル (Read Data Channel)

- 書き込みアドレスチャネル (Write Address Channel)

- 書き込みデータチャネル (Write Data Channel)

- 書き込み応答チャネル (Write Response Channel)

これらの独立したチャネルにより、読み取りと書き込みが効率的に処理されます。また、各チャネルが独立して動作するため、通信のオーバーヘッドが低減されます。

AXI の特徴

AXI は以下のような特徴を持っています。

- 高効率な通信: 複数のトランザクションを並行して処理することで、通信のパフォーマンスを最適化します。

- アドレスとデータの分離: アドレスとデータが分離されているため、読み取りと書き込みの操作が独立して行えます。

- 可変バーストサイズ: バースト転送のサイズを動的に変更でき、通信の柔軟性が向上します。

- 低遅延: パイプライン化によりデータ転送の遅延を最小限に抑えられます。

AXI の用途

AXI は主に以下のような用途で使用されます。

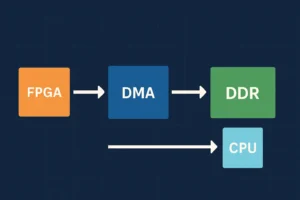

- プロセッサと FPGA の通信: ARM プロセッサ (PS) と FPGA (PL) 間でデータを転送し、PL 内のカスタムロジックを PS から制御することができます。

- IP コア間の接続: FPGA 内の異なる IP コア間でのデータ転送にも使用されます。

- メモリアクセス: メモリマッピングされたデバイスへの高速アクセスを実現します。

まとめ

AXI は高性能なチップ内通信を可能にし、FPGA や SoC のデザインにおいて非常に重要な役割を果たします。その柔軟性と効率性により、複雑なシステムのデータ転送を最適化し、通信オーバーヘッドを削減します。Red Pitaya のようなプラットフォームにおいては、AXI を活用することで PS と PL 間での高度な連携が可能になり、デバイス全体のパフォーマンスを向上させることができます。

FPGA の設計を行う際は、AXI の構造や特徴を理解し、実際のデザインに活用してみてください。